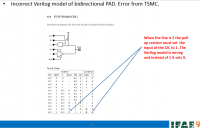

Modèle verilog incorrect pour PAD bidirectionnel (R.Casanova, juin 19)

Solution: le Cern à développé une librairie de Pads déboguées; à vérifier

Court-circuit sur plusieurs cellules buffer BUFTD (S.Drouet, nov.18)

Je viens de découvrir un problème sur la cellule numérique BUFTD24 (lib. tcb013ghp). La sortie Z est court-circuitée avec un net interne de la cellule. J'ai vu que la cellule BUFTD20 avait le même problème.

LVS errors with digital cells (N.Pillet, oct.18)

From: Nicolas Pillet nicolas.pillet@clermont.in2p3.fr Subject: Re: Update of CERN TSMC 65nm kit, what about the 130nm ? Date: 18 September 2018 at 17:09:08 CEST To: Kostas Kloukinas Kostas.Kloukinas@cern.ch

Dear Kostas,

We have some issues on the latest tsmc PDK : tsmc_cern_013_1.4c_3_b3. In the digital cells library, the cells CKNHVTD3+, CKNXHVTD3+, CKBHVT3+ (maybe more?) have parameters mismatchs. The diode “diodenhvt” area in the layout doesn't fit the area parameter in the schematic.

This issue only appears in the last version of the kit (in the beta3 not in the beta2). It seems that the area parameter in the schematic has been changed from 1.65E-13 to 1.75E-13 but the modification has not been done in the layout.

Do you know how this can be fixed ? Right now we are changing the standards cells layout to fit the schematic parameters but maybe there is a better option.

Cheers,

Nicolas

De: “Alessandro Caratelli” alessandro.caratelli@cern.ch À: “Nicolas Pillet” nicolas.pillet@clermont.in2p3.fr Envoyé: Mardi 23 Octobre 2018 15:03:12 Objet: RE: Update of CERN TSMC 65nm kit, what about the 130nm ?

Dear Nicolas,

… Regarding the LVS mismatch in the cells CKNHVTD3+, CKNXHVTD3+, CKBHVT3+, a possible approach could be to slightly increase the tolerance value to match the LVS, The problem is that this cell library and the lvs rule file comes from TSMC, so we can not in any case directly modify it.

If you notice any other bug or issue with the PDKs, please let me know,

Thank you,

Best regards, Alessandro