Outils pour utilisateurs

Panneau latéral

LVS errors with digital cells (N.Pillet, oct.18)

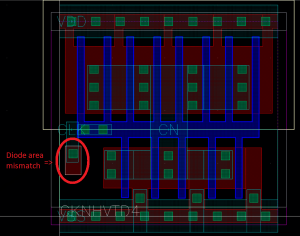

LVS mismatch sur diodenhvt, diodenlvt, dioden, pmos1vhvt, nmos1vhvt, …

KIT : tsmc_cern_013_1.4c_3_b3 Pour certaines cellules standards utilisant les diodenhvt, diodenlvt, dioden (ex : CKNHVTD3) Mismatch sur l'area de la diode (cf image). Il ya 5% de différence entre la schématique et le layout dû aux valeurs de width et length incorrectes dans les paramètres de la schematique.

Il est impossible de mettre les valeurs correctes pour ces paramètres : la largeur de la diode sur le layout est de 300nm alors que la valeur minimale acceptée dans la schématique est de 350nm.

Le problème a été remonté, réponse du CERN ci-dessous

From: Nicolas Pillet nicolas.pillet@clermont.in2p3.fr Subject: Re: Update of CERN TSMC 65nm kit, what about the 130nm ? Date: 18 September 2018 at 17:09:08 CEST To: Kostas Kloukinas Kostas.Kloukinas@cern.ch

Dear Kostas,

We have some issues on the latest tsmc PDK : tsmc_cern_013_1.4c_3_b3. In the digital cells library, the cells CKNHVTD3+, CKNXHVTD3+, CKBHVT3+ (maybe more?) have parameters mismatchs. The diode “diodenhvt” area in the layout doesn't fit the area parameter in the schematic.

This issue only appears in the last version of the kit (in the beta3 not in the beta2). It seems that the area parameter in the schematic has been changed from 1.65E-13 to 1.75E-13 but the modification has not been done in the layout.

Do you know how this can be fixed ? Right now we are changing the standards cells layout to fit the schematic parameters but maybe there is a better option.

Cheers,

Nicolas

De: “Alessandro Caratelli” alessandro.caratelli@cern.ch À: “Nicolas Pillet” nicolas.pillet@clermont.in2p3.fr Envoyé: Mardi 23 Octobre 2018 15:03:12 Objet: RE: Update of CERN TSMC 65nm kit, what about the 130nm ?

Dear Nicolas,

… Regarding the LVS mismatch in the cells CKNHVTD3+, CKNXHVTD3+, CKBHVT3+, a possible approach could be to slightly increase the tolerance value to match the LVS, The problem is that this cell library and the lvs rule file comes from TSMC, so we can not in any case directly modify it.

If you notice any other bug or issue with the PDKs, please let me know,

Thank you,

Best regards, Alessandro

Pour cela, rajouter les lignes suivantes dans les avCompareRules lors du LVS (pour Assura) afin d'ajouter une tolérance de 6% sur le paramètre area des diodes.

:gen: compareParameter(“diodenhvt” percent(“area” 6))

:gen: compareParameter(“diodenlvt” percent(“area” 6))

:gen: compareParameter(“dioden” percent(“area” 6))

Des problèmes similaires sont également présent sur les pmos1vhvt et nmos1vhvt sur le paramètre width. Le mismatch ici est très faible (<0.3%) Lignes à ajouter pour mettre une tolérance de 0.3% :

:gen: compareParameter(“pmos1vhvt” percent(“w” 0.3))

:gen: compareParameter(“nmos1vhvt” percent(“w” 0.3))

Il est possible que d'autres cellules soit impactées. Pour les valeurs de tolérance il se peut qu'elles soient revues à la hausse étant donné que toutes les cellules standards n'ont pas été verifiées.

Joinable nets (Echange de mails entre L.Leterrier-R.Vandaele, oct.18)

Bonjour Laurent,

En ce qui concerne ton soucis hiérarchique, je n'ai pas souvenir d'avoir rencontré ce genre de désagrément. Il faut dire que j'évite souvent d'utiliser et de “trainer”cette connexion virtuelle trop longtemps dans ma hiérarchie. Bonne journée

Le 01/10/2018 à 11:12, laurent leterrier a écrit :

Bonjour Richard,

Merci pour cette réponse très détaillée.

J'ai essayé et ça marche !

Il reste encore pour moi un grand mystère, je t'explique :

Sur mon niveau hiérarchique le plus bas, ta méthode fonctionne parfaitement.

Dès que je passe sur un niveau hiérarchique supérieur, j'ai certaine fois des erreurs et d'autres fois pas d'erreur alors que je n'ai rien changé ! Sur ces niveaux, le LVS peut passer même si je ne duplique pas les pins mais pas à chaque fois. Un layout qui passe le LVS à un instant t, peut ne plus passer 1 minute plus tard alors que je n'ai rien changé ! As-tu déjà eu ce comportement particulier suspect ?

Bonne journée.

Laurent.

De: “Richard VANDAELE” richard.vandaele@clermont.in2p3.fr

À: “Leterrier Laurent” leterrier@lpccaen.in2p3.fr

Cc: “Laurent ROYER” royer@clermont.in2p3.fr, “Richard VANDAËLE” vandaele@clermont.in2p3.fr

Envoyé: Jeudi 27 Septembre 2018 11:54:28

Objet: Re: question bb130 assura

Bonjour Laurent,

Désolé pour la réponse tardive.

Je suis justement en train de réaliser un layout et j'ai eu besoin de réaliser un joinableNet.

Déjà je peux te dire que cela fonctionne.

Comme je ne sais pas comment tu as utilisé cette fonction, je vais reprendre du début.

Tout d'abord, il faut dupliquer ta pin. Typiquement dans mon cas j'ai plusieurs rails d'alim qui ne sont pas interconnectés. Je copie donc la pin “VDD” sur chacun des rails “isolés”.

Ensuite dans la fenêtre LVS d'Assura j'active la fonction “Use joinableNet Function”

Ensuite tu cliques “Modify joinableNet Function”

Ensuite tu renseignes la cellule sur laquelle tu souhaites réaliser la connexion virtuel entre tes pins, puis tu indiques le nom des nets impactées.

Ensuite tu cliques sur “Add to Command List”

Et voilà, reste plus qu'à lancer le LVS !!

Si jamais tu as toujours tes erreurs, tiens moi au courant !

Bonne journée

Bonjour,

J'ai une petite question au niveau du kit TSMC130. J'ai un layout où je souhaite connecter des pins ensemble virtuellement (ces pins seront reliées sur un niveau hiérarchique supérieur). Sous le kit AMS, j'utilisais la fonction “joinableNet” sous Assura (LVS). Avec le kit TSMC130, je n'arrive pas à l'utiliser (génère des erreurs). As-tu déjà utilisé cette fonction en TSMC130 ? Si oui, peux-tu m'indiquer comme faire ?

Cordialement,

Erreurs LVS pins et vias sur bloc numérique (L.Royer, mars 18)

Les blocs numériques créés avec Encounter doivent être rattachés à une librairie dont la propriété de techLibName est tcb013ghp. Cette librairie contient les vias utilisées par Encounter. Une librairie Digital a été créée pour contenir tous les blocs numériques de BB130.

Erreur LVS sur les drivers SLVS de "Marek" (E.Bechetoille, dec.17)

Je voulais entreprendre d'utiliser les drivers de Marek, mais le LVS ne passe pas. Quelqu'un connais la raison ? On dirait qu'il a mis des diodes pour faire passer des erreurs d'antenne, mais je ne suis pas sûr.

- ERROR* Device 'dio_pwdnw(DIO)' on Schematic is unbound to any Layout device.

- ERROR* Device 'dio_dnwpsub(DIO)' on Schematic is unbound to any Layout device.

- ERROR* UnBound devices found.

Salut Édouard,

Il s'agit des diodes dues au Deep Nwell. Tu peux les extraire (turn on switch : extract_parasitic_diodes dans le fichier calibre.lvs), il faut alors les ajouter dans ton schéma. C'est pour voir la contribution des diodes parasites des Wells P, N et Deep.

Damien

Assura : Set Switches : compare_parasitic_diodes extract_parasitic_diodes → [MATCH] !!

Merci Damien :

MAJ : /!\ quand on mets les switch *_diodes, ensuite l'extract ne marche pas. Il faut repasser un LVS sans les switch pour pouvoir passer QRC. (E.Bechetoille, nov.18)

PADs de la librairie tpa013nv3: erreurs LVS (R.Vandaele, D.Thiepont, dec.17)

voir l'article ici

Configuration Assura pour DRC, LVS et QRC (M.Dahoumane, dec.17)

Supprimer short LVS avec symbole CDS_Thru (R. Vandaele, nov.2020)

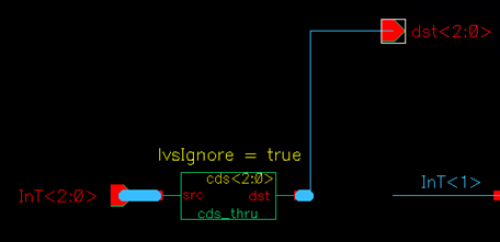

Sur une vue top, l’utilisation de cds_thru avec 2 pins (1ère en entrée et la 2ème en sortie) peut générer une erreur de short lors du LVS. En effet le le symbole cds_thru permet sur une schématique de réaliser un changement de nom de net.

Par exemple InT<2 :0> deviens dst<2 :0>.

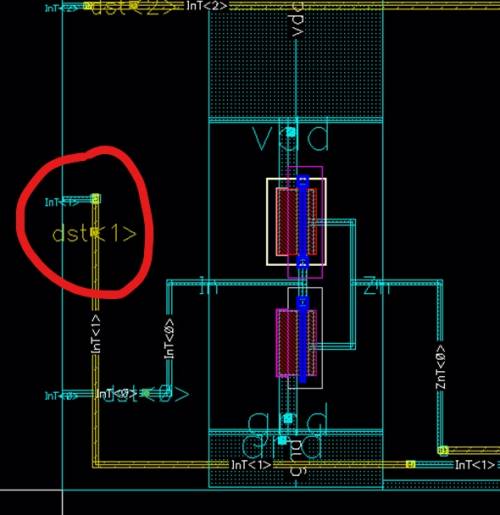

Toutefois au niveau layout cette cellule n’existe pas (elle n’a pas de correspondance physique) et layout XL nous oblige à placer les pins InT<1> et dst<1> sur la même piste.

En faisant cela, le LVS nous indique un short entre ces 2 pins. Pour éviter cette erreur lors du LVS, il est nécessaire de renommer virtuellement les dst<i> en InT<i>. Pour cela il est nécessaire de créer un usr.pvl rule file dans lequel je renomme les nets incriminées : layout_rename_text “/dst<2>/InT<2>/” -database layout_rename_text “/dst<1>/InT<1>/” -database layout_rename_text “/dst<0>/InT<0>/” –database

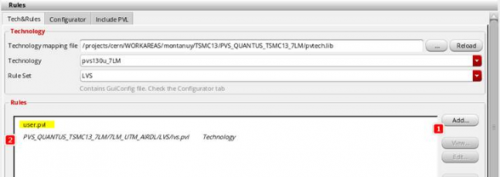

Ce fichier usr.pvl est ensuite renseigné dans la fenetre Rules 1 – Bouton Add à Browser 2 – user.pvl

A la suite de cela, les erreurs de short liées au cds_thru disparaissent.